Ce thread liste les précautions à prendre et/ou vérifier avant de se lancer dans un upgrade vers une connectivité 10Gb/s. Une telle connexion représente un flux pouvant aller jusqu'à 1,2Go/s, l'impact est très important en regard des ressources disponibles sur une carte mère. D'autant plus que ce flux doit bien aller quelque part au final.

"Moi aussi je veux ça" Choix du bus

Choix du busLe bus PCI standard était déjà juste suffisant(*) pour le Gigabit. En version 64bits (533Mo/s) ou même PCI-X (1066Mo/s), ce n'est pas suffisant non plus.

*: à condition de trouver la bonne carte, cf

https://lafibre.info/infrastructure/carte-reseau-1-gbs-limitee-a-500-mbs/Le bus PCI-Express supporte couramment 3 normes sur nos cartes mères actuelles:

- 1.0/1.1: taux de 2,5GT/s soit

250Mo/s par ligne

- 2.0: taux de 5GT/s soit

500Mo/s par ligne

- 3.0: taux de 8GT/s soit

984,6Mo/s par ligne

Prochaines versions (non implèmentée ou en cours de finalisation):

- 4.0: taux de 16GT/s soit

1969Mo/s par ligne

- 5.0: taux de 32GT/s soit

3938Mo/s par ligne

Attention: il s'agit du débit brut, pas du débit utile. Le protocole PCI-Express a en effet un overhead.

Le nombre de lignes utilisables suit cette règle: x1, x2, x4, x8 et x16. En pratique, on ne trouve jamais de x2.

Les connecteurs courant sont

x1, x4, x8 et

x16. Attention, il s'agit d'une taille physique ! En effet, la norme PCI-Express prévoit une rétro-compatibilité: un périphérique x1 peut être utilisé dans un slot x16. Pour faire l'inverse il suffit d'un adaptateur ou que le slot ne soit pas pourvu d'encoche.

Ainsi, toutes les lignes ne sont pas forcèment câblées, soit pour une question de coût, soit car il n'y en a plus de disponibles.

Dans le reste de ce thread, la notation PCIe sera utilisée.

Northbridge ou Southbridge ?Jusqu'en 2008/2009, les processeurs d'Intel faisaient appel à un chipset pour communiquer avec le monde extérieur, on l'appelle le "Northbridge". Ce chipset était une puce en charge:

- des accès mémoire

- du connecteur graphique dédié (AGP puis PCIe)

- ou éventuellement d'un chipset graphique intégré

- de la connexion avec le "southbridge", via une connexion dédiée (PCI au début puis DMI à la fin)

- parfois en option un contrôleur Ethernet

Chez Intel, le Northbridge a l'acronyme de

MCH pour Memory Controller Hub

https://en.wikipedia.org/wiki/Northbridge_(computing)Le "Southbridge" était à son tour en charge des connexions avec les périphériques dits "lents", c'est-à-dire:

- contrôleur IDE ou SATA pour les disques durs

- contrôleur USB

- contrôleur audio AC'97

- bus I2C

- bus PCI

- contrôleur Ethernet

Chez Intel, le Southbridge est connu sous l'acronyme "

ICH" pour I/O Controller Hub

https://en.wikipedia.org/wiki/I/O_Controller_Hub.

Cette architecture a rapidement atteint 2 limites:

- le bus Processeur <-> MCH, dit FSB (Front Side Bus), limite les accès vers la mémoire et la carte graphique

- le bus MCH<->ICH limite à son tour les échanges avec l'extérieur.

Un seul chipsetComment faire ? Simple:

- migration du contrôleur RAM dans le CPU

- intégration du connecteur graphique PCIe x16 dans le CPU

- création d'un bus normalisé entre le CPU et le Southbridge

Oups pardon, le

PCH, Platform Controller Hub

https://en.wikipedia.org/wiki/Platform_Controller_HubLes accès mémoires sont désormais plus rapide, du fait de la latence réduite par l'accès direct et parce qu'il est assez simple d'augmenter la bande passante mémoire en jouant sur le nombre de contrôleur (1 seul au début, puis 2, 3 et même 4 aujourd'hui).

Autre avantage de la solution, Intel a pu intégrer directement un contrôleur graphique dans ses processeurs.

Intel a même été plus loin en intégrant le PCH au sein du processeur sous la forme d'un SoC unique.

"Chouette, fini les problèmes de bande passante !"

Pas tout à fait, si on a réglé le problème de la mémoire et du bus graphique, il reste toujours une connectivité à améliorer vers l'extérieur.

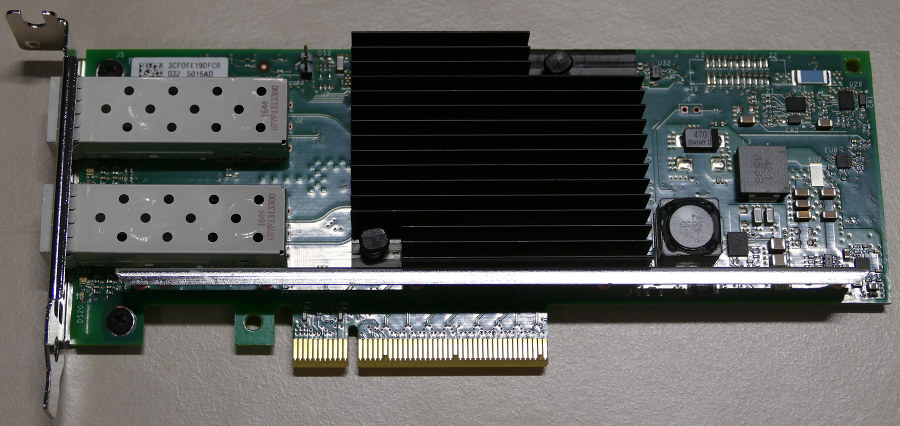

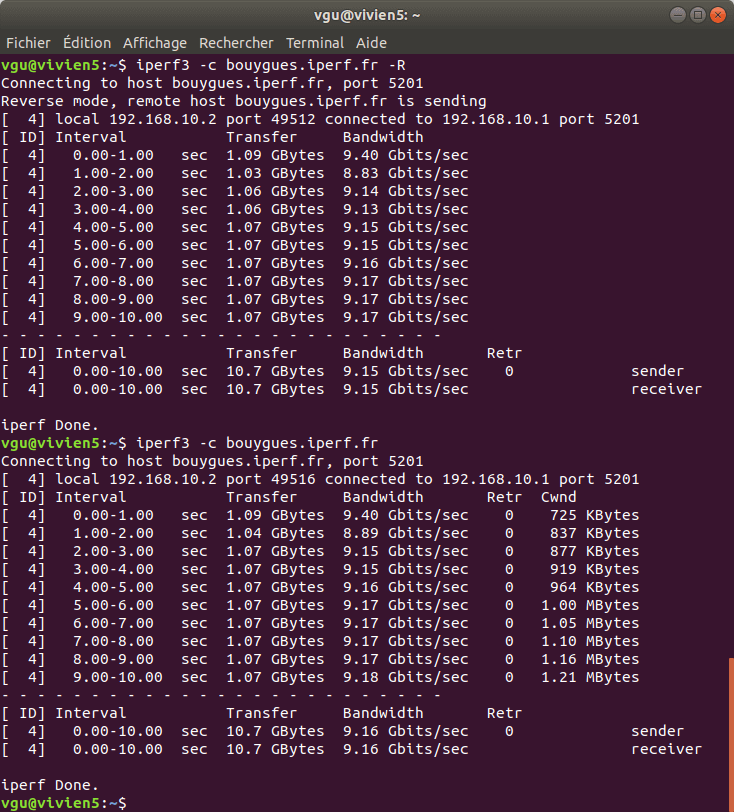

Explique-moi ton besoin, je te dirais comment t'en passerAu minimum, une carte réseau 10Gb/s a besoin de 4 lignes PCIe 2.0. En 1.1, on n'a que 1000Mo/s théoriques donc ça ne sera pas suffisant, il faudrait alors 8 lignes PCIe 1.1.

Ainsi on trouvera des cartes PCIe 2.0 x8: grace à la rétro-compatibilité, en PCIe 1.1 elles auront suffisamment de bande passante pour 1x 10Gb/s.

En revanche, s'il y a 2 ports 10Gb/s, le PCIe 3.0 devient obligatoire sur 4 lignes.